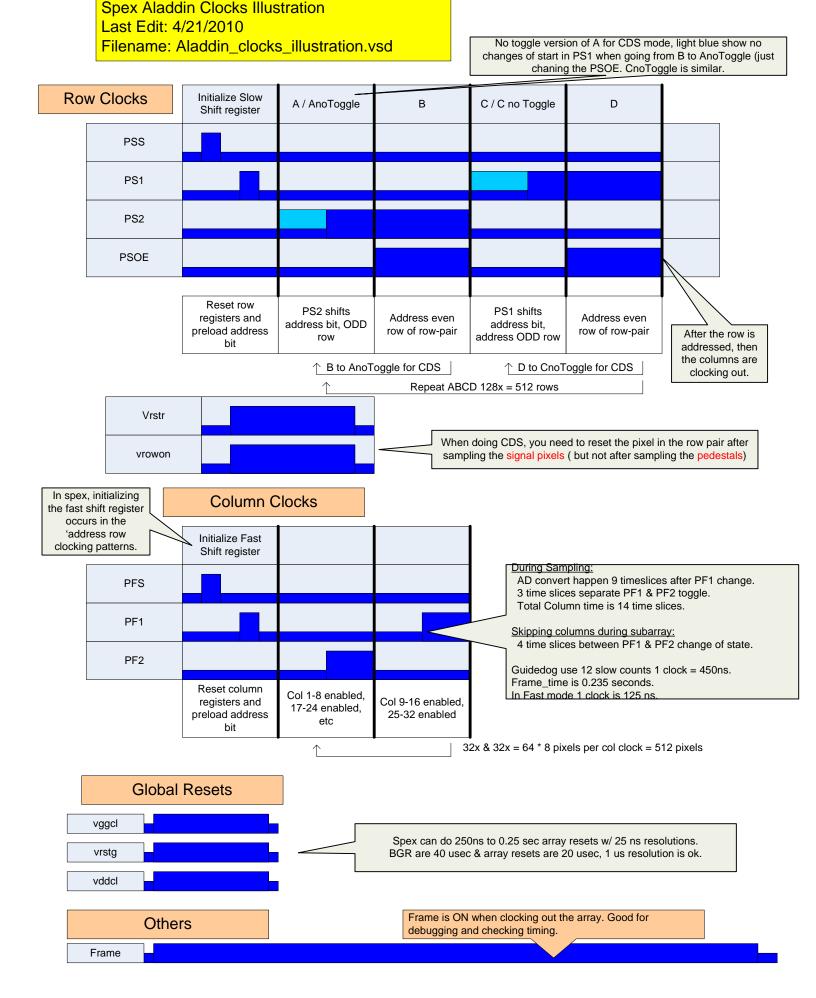

<u>Current Spex row timing:</u> Guidedog's FASTMODE is 125 ns TimeSlices

GuideDog's default is 12 slowcnt or 450 ns TimeSlices

When sampling Column, we used 35 TS: 9 TS before converts, and 3 between PF1/PF2 toggle.

Can we used slowcnt with the SGIR pattern generator? Yes, based on 35 TimeSlice, we can do this:

| USING SG | IR SLOW   | CNT: $ns = 40 +$ | (20*slowcn | t)        |  |  |  |

|----------|-----------|------------------|------------|-----------|--|--|--|

| Slowcnt  | slowcnt_n | s Pattern        | Fram       | e_Rate ms |  |  |  |

| 4        | 120       | 4200             |            | 68.8128   |  |  |  |

| 20       | 440       | 15400            | 2          | 52.3136   |  |  |  |

|          |           |                  |            |           |  |  |  |

Clock the row and convert. Aladdin we group 2 column in a pattern generator, 16 pixels (8channell \* 2 ):

|            |                 |        | J                                                    | •      |        |        | U     |       |       | `      | ,  |  |  |

|------------|-----------------|--------|------------------------------------------------------|--------|--------|--------|-------|-------|-------|--------|----|--|--|

|            |                 | 0      | 1                                                    | 2      | 3      | 4      | 5     | 6     | 7     | 8      |    |  |  |

| PG3        | b0              |        |                                                      |        |        |        |       |       |       |        |    |  |  |

|            | b1              |        |                                                      |        |        |        |       |       |       |        |    |  |  |

|            | b2 PFS          |        |                                                      |        |        |        |       |       |       |        |    |  |  |

| PG4        | b0 - PF1        |        |                                                      |        |        |        |       |       |       |        |    |  |  |

|            | b1- PF2         |        |                                                      |        |        |        |       |       |       |        |    |  |  |

|            | b2 - vclamp     |        |                                                      |        |        |        |       |       |       |        |    |  |  |

|            | b3 -ADCTRIG     |        |                                                      |        |        |        |       |       |       |        |    |  |  |

|            |                 |        |                                                      |        |        |        |       |       |       |        |    |  |  |

| Spex TS    |                 | 3      | 9                                                    | 1      | 4      | 3      | 9     | 1     | 4     | 1      | 35 |  |  |

| To get sim | nilar Timing we | can d  | o this:                                              |        |        |        |       |       |       |        |    |  |  |

| SGIR       |                 | 3      | 9                                                    | 2      | 2      | 3      | 9     | 2     | 2     | 1      | 33 |  |  |

|            |                 | Yello  | w bloc                                               | k timi | ing de | termir | ne by | ADC I | param | eters, | ı  |  |  |

|            |                 | This e | This example uses 2 or 220 ns (2 samples, 1 channel) |        |        |        |       |       |       |        |    |  |  |

|            |                 |        |                                                      |        |        |        |       |       |       |        |    |  |  |

Yellow assumes 1 ch, 2 sample or 110ns\*2 = 220. That's equivalent to 2 120 ns timeslices (240ns)

That means, slowcnt and numsample defines the timing.

Clock a row with no converts: to clock quickly over row (used for subarrays)

|            |                 | 0     | 1      | 2 | 3 | 4 | 5 | 6 | 7 | 8 |    |

|------------|-----------------|-------|--------|---|---|---|---|---|---|---|----|

| PG3        | b0              |       |        |   |   |   |   |   |   |   |    |

|            | b1              |       |        |   |   |   |   |   |   |   |    |

|            | b2 PFS          |       |        |   |   |   |   |   |   |   |    |

| PG4        | b0 - PF1        |       |        |   |   |   |   |   |   |   |    |

|            | b1- PF2         |       |        |   |   |   |   |   |   |   |    |

|            | b2 - vclamp     |       |        |   |   |   |   |   |   |   |    |

|            | b3 -ADCTRIG     |       |        |   |   |   |   |   |   |   |    |

|            |                 |       |        |   |   |   |   |   |   |   |    |

| Spex TS    |                 | 4     | 4      |   |   | 4 | 4 |   |   | 0 | 16 |

| To get sim | nilar Timing we | can d | o this | : |   |   |   |   |   |   |    |

| SGIR       |                 | 4     | 2      | 1 | 1 | 4 | 2 | 1 | 1 | 1 | 17 |

To initialize fast shift register, we need to reprogram PG3 / 4. This will happen 1 once evey row

|            |                  |       |        |         |      |   |   |   |   |   | -  |

|------------|------------------|-------|--------|---------|------|---|---|---|---|---|----|

|            | b2 PFS           |       |        |         |      |   |   |   |   |   |    |

| PG4        | b0 - PF1         |       |        |         |      |   |   |   |   |   |    |

|            | b1- PF2          |       |        |         |      |   |   |   |   |   |    |

|            | b2 - vclamp      |       |        |         |      |   |   |   |   |   |    |

|            | b3 -ADCTRIG      |       |        |         |      |   |   |   |   |   |    |

|            |                  |       |        |         |      |   |   |   |   |   |    |

| Spex TS    |                  | 4     | 4      | 4       | 4    | 4 | 0 | 0 | 0 | 0 | 20 |

| To get sim | ilar Timing in S | GIR v | ve car | า do tl | nis: |   |   |   |   |   |    |

| SGIR       |                  | 4     | 4      | 4       | 4    | 1 | 1 | 1 | 1 | 1 | 21 |

## Clocking Rows

There are 4 signal used to control the Row MUX: PSS, PS1, PS2, PSOE

PS1, and PS2 are used to march the address bit on the MUX. This address bit address a row-pair: AB or CD.

Then the PSOE is used to select one of the row pairs.

It is best to used DIGOUT for the row mux signal. (rather that the parallel pattern generator)

| PSS     |   |   |   |   |   |   |       |  |

|---------|---|---|---|---|---|---|-------|--|

| PS1     |   |   |   |   |   |   |       |  |

| PS2     |   |   |   |   |   |   |       |  |

| PSOE    |   |   |   |   |   |   |       |  |

|         |   |   |   |   |   | - | Total |  |

| spex TS | 1 | 4 | 4 | 4 | 4 |   | 17    |  |

|         |   |   |   |   |   |   |       |  |

| SGIR TS | 1 | 4 | 4 | 4 | 4 |   |       |  |

Here we intialize the row mux, by toggling SS(slow sync) and the S1. SGIR will do the same using DIGIOUT and Delays.

|         | Row | A  |   | Row | В | Row | С | Row | D |                         |              |           |  |

|---------|-----|----|---|-----|---|-----|---|-----|---|-------------------------|--------------|-----------|--|

| PSS     |     |    |   |     |   |     |   |     |   |                         |              |           |  |

| PS1     |     |    |   |     |   |     |   |     |   |                         |              |           |  |

| PS2     |     |    |   |     |   |     |   |     |   |                         |              |           |  |

| PSOE    |     |    |   |     |   |     |   |     |   |                         |              |           |  |

|         |     |    | * |     | * |     | * |     | * | * = columr              | ns are reado | out here. |  |

| spex TS | 4   | 18 |   | 18  |   | 18  |   | 18  |   | Spex used               | 18 TS bec    | ause the  |  |

|         |     |    |   |     |   |     |   |     |   | fast MUX a              |              |           |  |

| SGIR TS | 4   | 8  |   | 8   |   | 8   |   | 8   |   | Can be as fast as 4 TS. |              |           |  |

|         |     |    |   |     |   |     |   |     |   |                         |              |           |  |

The above table show how we can used DIGOUT to march the Row Address Bit down the Row (slow) MUX. For SGIR we will not do CDS mode (just fowler sampling), so the CDS scheme will not be illustrated, but can easily be accomplished.

| Vrstr   |   |    |   |  |  |

|---------|---|----|---|--|--|

| vrowon  |   |    |   |  |  |

|         |   |    |   |  |  |

| Spex TS | 2 | 16 | 2 |  |  |

Just for completeness, the Vrstr, and vrowon are used to reset the pixels in the row pair during CDS mode. The TS used in spex is displayed here.